グランドノイズと聞いて、どんなイメージを持たれるでしょうか?

機器のグランド(アース)電極を介して機器の様々なところへ流れ込んで、予期せぬ場所から空間に出ていくのでは、、、等と考えて、EMC対策としてグランドノイズは低減すべきもの、と考えておられる方もいるでしょう。

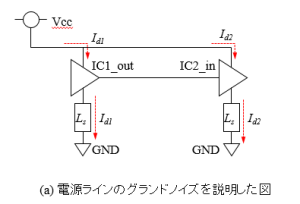

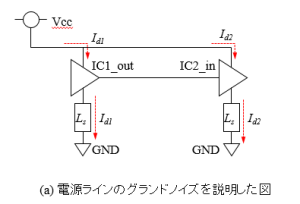

グランドノイズに関してはEMC関連のハウツー本やWEB等でよく解説されています。ここで簡単に説明しますと図(a)に示すようにICが電源ラインとGND電極に接続する際、IC内の特に出力バッファーの動作(Lowレベル⇔Highレベルの遷移)において瞬間的に電源(Vcc)側からGND側へ貫通電流が流れます。この時、IC内のバッファーと回路基板上のGND電極の間に介在する寄生インダクタンス(Ls)により電圧が発生し、これがグランドノイズとなります。

正確には、電源(Vcc)側の配線においても寄生インダクタンスが存在しますので、その寄生インダクタンスも含めてグランドノイズとされている方もいます。また、Vcc側の電源配線を介してIC外部に漏洩していくイメージから、電源ノイズとしている方もいます。当方としましては、ノイズであっても活線とGNDの2極により伝導する電源ラインのノイズと考えています。

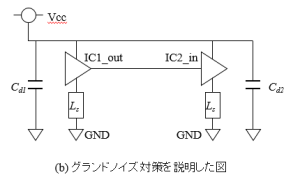

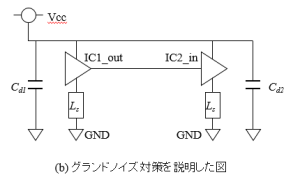

さて、このノイズの対策としては図(b)に示すようにパスコンCd(デカップリングコンデンサ)を用います。パスコンCdにより、VccとGND間の交流(高周波)電位を0V(交流短絡)にすることにより寄生インダクタンスLsによるノイズ電圧の発生を抑制させます。しかし、実際のパスコンCdには寄生インダクタンスがあることや、パスコンとIC内バッファーとの間の接続においてインダクタンス成分があったりすることで、前述の交流短絡の効果が低下します。その対策として、パスコンに寄生インダクタンスの低減を目的としたLW逆転型や三端子型といった特殊なパスコンを適用させたり、ICとパスコンの間の配線に伴うインダクタンスを低減するICパッケージやパスコンの実装方法を適用させたりといった多くの方法があります。

一般的に、低クロックのCMOS ICであれば、電源パスコンを必要とするものの、あまり前述のような寄生インダクタンスを気にする必要はなく、即ちグランドノイズの発生を考慮する必要はありません。しかし、高クロックのCMOS ICとなると上記のような特殊なパスコンを検討する必要が出てくる場合もあります。

ただ、押さえておくべき点として、パスコンの実装によりパスコンの接続した点でのノイズ(高周波)帯域で十分に交流短絡(電気回路的には0Vとなることは無いので電圧値としては-40dBV (=0.01V) 以下と言った値を目指すことになります)ができているか、と言うことです。

PIの通常の評価では指標としてICの電源端子側からみた電源側のインピーダンス(インプットインピーダンス)をICが安定動作する(とされる?)ターゲットインピーダンスよりも低くなるようにパスコンの選択と個数の調整等を行います。実際の現場ではターゲットインピーダンスが分からないことが多くインプットインピーダンスをできるだけ低くして、それにより高周波のノイズ帯域で十分に0Vに近づくようにしています。

しかし、電源ラインの途中に回路基板間を接続するケーブルが介在する場合は、上述のPIでの評価では十分ではない場合があります。PIを検討できる市販のツールでは複数の回路基板及びそれらを接続するケーブルからなる電源系におけるPIの評価を対象とはしていないからです。実際のEMI対策の経験を通して、電源系のEMI(不要輻射)ではケーブル起因によって生じている場合が多いのです。

当社のPDは電源ケーブルを含んで電源系のノイズを評価することができます。詳細説明は”PD適用・実践編”でご紹介しますが、回路図の段階で電源ラインにおけるEMI設計のために取るべき対策及び検討方法(シミュレーション)について解説します。

ここで簡単にグランドノイズに関してまとめますと

①グランドノイズとはICの電源端子及びGND端子接続部に寄生するインダクタンスより生じる電圧ノイズです。

②グランドノイズはICに接続させる電源パスコン(デカップリングコンデンサ)により対策されています。

③パスコンの最適化設計はPI評価により行うことができます。

④但し、回路基板間をケーブルを介して電源供給が行われる場合は当社のPDを適用して電源ラインの設計を行うことを強くお勧めします。

※関連ページ