アーカイブ

35. EMC設計と回路のインピーダンス、如何なる関係?

高周波回路関係やEMC関連に携わるようになった方々は、多分その職場の古参の先輩から回路図や回路基板を見てインピーダンスが高い(or低い)ネェ、といった言葉を漠然と聞くことがあるでしょう。もっと短縮してハイインピー/ローインピーと言われることもあるでしょう?

高周波回路の設計を経験したことのある方は分かると思いますが、回路設計における基本のインピーダンスを50Ωとして考える癖がついているので、50Ωを下回るインピーダンスはローインピー、100ないし200Ωを上回るとハイインピーと言う傾向があるのではないか、と思います。勿論、個々人により解釈は変わりますが、ただこの時のインピーダンスは高周波に対するキャパシタンスやリアクタンスといった複素成分に対して評価しており、キロΩレベル以上は高周波にとっては実質的に絶縁していると考えます。尚、実数成分となるレジスタンスに対しては振幅抑制という観点と実損失という観点から積極的に評価したり、また状況によりしなかったりではないかと思います。

回路におけるインピーダンス評価は主として電源出力部、伝送路、終端部の負荷に対する傾向評価となっているかと思います。ただ単位がΩとなるため、どうしても抵抗をイメージしてしまうかもしれませんが、単純に各部位で電圧と電流の比がどうなっているのかを評価している、というように考えましょう。

一般的な評価として、

電源部では、ローインピー➡電源能力が高い/ハイインピー➡電源能力が低い

終端部では、ローインピー➡重い負荷/ハイインピー➡軽い負荷

となります。では伝送路に関してはどうなのかというと、

伝送路では、ローインピー➡耐ノイズ性が高い/ハイインピー➡耐ノイズ性が低い

となります。だからどうするということはここでは解説しませんが、これら3つの部位に対して、

EMC性能としては、ローインピー➡EMC性能が高い/ハイインピー➡EMC性能が低い

と、あくまで一般論ですが、傾向として評価できます。特に、伝送路に関しては、空間インピーダンス(電波伝搬のインピーダンス)となる377Ωが意識され不要輻射の原因となる場合があります。

とまあ、一般論を述べましたが、EMC設計の上ではこういったインピーダンスをどう考慮すべきでしょうか?基本的には高周波設計と同様に各部位間でのインピーダンス整合が取れるように回路設計及び配線設計を行うこととなります。但し、アナログ(RF)とデジタル(CMOSロジック)では信号帯域に対する考え方が異なります。

アナログでは対象周波数(狭帯域)に対してインピーダンス整合をとることが最重要となります。これに対し、CMOSロジックでは好ましい電圧波形を得るための周波数帯域の抑制が重要になります。そういった操作・調整を行うことが、結果としてCMOSロジックに対してインピーダンス整合を行ったことになります。そのため、アナログのインピーダンス整合設計のためにLC素子を使いますが、CMOSロジックではLC素子を使わないのが通常です。しかしながら、CMOSロジックのノイズを何とか抑え込むためでしょうか、ビーズやコンデンサが使われている例を目にすることがあります。必死になって対策を行ったのでしょうが、少しでも回路設計・配線設計を見直す時間があればもっとシンプルな形態で解決できたのではないか、などと思ったことがあります。

実際のEMC対策の現場ではどの程度のインピーダンス(値)の設計が適当なのかはそれぞれの状況によるので、定量的には定まるものではありません。しかし、そのような状況であってもシミュレーションが利用できれば、EMC性能の傾向とインピーダンスの状況を数値的に解析することができます。当社がご紹介している、PD適用、SD適用は、将にそう言ったインピーダンス値を取得できる方法なのです。是非ご参考にして下さい。

※関連ページ

PD適用に関する技術資料

SD適用に関する技術資料

WD提案に関する技術資料

EMC設計 MBDでDX! 技術&学術

34. ベタGNDの2点間を流れる電流は最短距離、は間違い。

電源ラインや信号ラインの電流の流れ方については、当ホームページの“25. これがグラウンド(GND)を流れるリターン電流!”でも解説してきましたが、Hot側電極とGND側電極との間で反平行(⇄)の形態で流れることを解説しました。

しかしながら、EMC関係の一部のセミナーや記事等では、ベタグラウンド(GND)に流れる電流について、直流や低周波では最短距離で電流が流れ、高周波ではHot側の配線に沿って流れるとか、またはその逆に高周波でこそ最短距離で電流が流れるといったことが語られており、本当はどうなのかについて検討してみました。

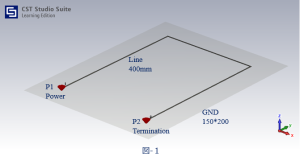

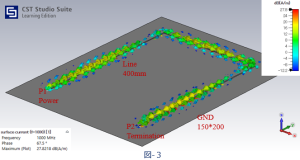

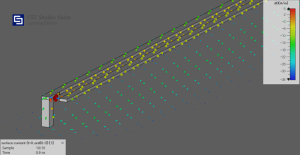

そこで、電磁界シミュレータ(CST Studio Suite LE)を使ってベタグラウンドに流れる電流について検討してみることにしました。下記の図1はシミュレーションに用いたモデルでベタGND電極の形状は150 *200 (mm)、Hot側電極(Line)は幅1mmで長さが400mmとしGNDとLine間の距離(Z方向)は1mmとしました。このLineとGND間に配置する第1ポートを電源、第2ポートを終端抵抗にして計算を行いました。

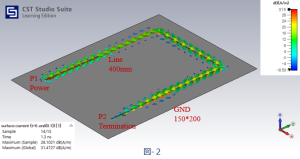

先ず、電源を直流(DC)とした時の電流の流れの状況を図2に示します。

図2では、第1ポートと第2ポート間のGND電極上の電流の流れ方はLineに沿って上述したように反平行(⇄)の形態で流れており、第1ポートと第2ポート間の最短距離で電流は流れていないことが分かります。

次に、電源を高周波(1GHz)とした時の電流の流れの状況を図3に示します。

図3においても第1ポートと第2ポート間のGND電極上の電流の流れ方はLineに沿って反平行(⇄)の形態で流れており、第1ポートと第2ポート間の最短距離で電流は流れていないことが分かります。

以上のことから、ベタグラウンド(GND)に流れる電流は常にHot側の配線(Line)に沿って流れるのです。

これは、Hot側電極を流れる電荷に対してGND電極側にはその電荷の反対極性の電荷が流れ、それらはクーロン力によって常に引き合っているためと考えられます。

こう言いますと、物理で電流を理解されている方は、“電流は、本当は電子の流れでしょ!”と言われるかもしれません。確かにその通りですが、電源はその一方の極から電子を出す際、必ずその電源の他方の極より電子の取り込みが行われますので、この電子の取り込みは正孔(電子の欠陥)をその電源の他方の極より出しているのと同等になります。即ちこの正孔が正の電荷に相当し、電子は負の電荷ですので、前述のクーロン力の考え方と矛盾しない、ということになります。

上記した“GND電極上の電流の流れはHot側の配線(Line)に沿って流れる”という考え方を積極的に回路基板設計(A/W)で活かそうとするのが、当社の“WD(Wiring Board Design for EMI)提案”です。詳細につきましては、当社のセミナーでご紹介しております。

※関連ページ

9.ノイズ電流の流れ方。その前に前提のモデルを考えて。

6.コモンモード電流・リターン電流とEMIの関係、如何なるモデルか?

25.これがグラウンド(GND)を流れるリターン電流!

31.電源・信号ラインに対向するGND電極の幅は広い程よい、って本当?

5.回路基板におけるEMC設計の実践と検図。当社のWDを提案。

WDに関する技術資料

33. ESD試験で被試験機に不具合発生・・・原因は火花放電の高周波成分➡IC故障

当ホームページではESD試験(IEC-61000-4-2)における不具合発生に関して、 “サージ関連試験での不具合対策は試験パルス印加による2次放電発生も勘案して”や“27. ESD試験時の2次放電発生の予見・・・simで確認。これが不具合原因!”等で、ESD試験でのESDパルス印加後の被試験機内の2次的な火花放電発生が原因となっていることを指摘してきました。しかしながら、その2次的な火花放電発生が如何にして被試験機の不具合を発生させているかについてはあまり明確な説明をしてきませんでした。

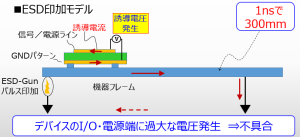

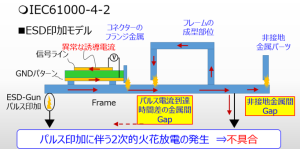

このページではその不具合発生に関して考察してみます。先ず、当方の資料“ESD試験(IEC61000-4-2)対策に関する技術資料”の中でESDパルス印加後における特に回路基板内での電源・信号ラインとGND電極パターン間で誘導電圧が発生するメカニズムを解説した部分があります。(下図)

この図はESDガンにより電流パルスが被試験機のフレームや回路基板のGND電極に流れ込んでいる状況です。この時回路基板でGND電極に沿って配置される電源ラインや信号ラインにはGND電極側を流れる電流により生じる磁界に対してその磁界を打ち消す方向に流れる電流が誘導され、その誘導によってGND電極に対して電源ライン・信号ラインに電圧が発生する、ということを説明しています。これは電磁界SimやSPICE等で解析することができ、ESDガンの設定電圧を4KVにして接触印加をすると、GND電極と各ライン間に+/-40V程度(ライン側の長さにもよる)の電圧変動が生じたりします。

ただ、この電圧変動は50ns以下程度の時間の減衰振動なので、例えばICが8MHzのクロック動作の場合は、1パルスが125nsなので半パルスに満たない時間でESDガンの影響はなくなりますが、実際はこの程度のクロックのICでも不具合を起こしてしまいます。実際のロジックの設計では何等かのチェック/リカバリ/リトライ等を行ってシステムの堅牢(ロバスト)性を確保していますので、ESDガンによる印加パルスがロジックのシステムを直接破綻させる可能性は低いと思われます。

そこで疑われるのがIC内の半導体構造自体への影響です。私がかつてIC設計に携わっていた頃、半導体の基板(サブストレート)上に複数のトランジスタを配置してそのデザインチェックをした際に出る“ラッチアップ”のエラーに悩まされた経験があります。これは、サブストレート内の小さな領域(プロセスデザインキットによるルール)にpnpn構造ができてしまっていることを警告するものです。pn構造と言えばダイオードが思いつくでしょう。pnpn構造はサイリスタと呼ばれ、条件によりそのサイリスタがON状態(ラッチアップ)となりpnpn方向に過大な貫通電流が流れ、ICのロジックは破綻し、その電流量によっては半導体素子が破壊してしまいます。このサイリスタは一旦ONになってしまうとその状態が保持されてしまうため、一旦全電源をOFFする必要があり、電源を再投入すれば、運が良ければシステムは再起動します。しかし、この状況を繰り返すとICは故障の状態になっていきます。

そこで、上記したサイリスタがONする条件ですが、電圧の時間変化:dV/dtが大きいパルス状のノイズがICの信号入力端に入った場合や、ICの電源端側の電圧変動で電圧が低下したタイミングで電源端側より高い信号の入力が生じた場合に起こります。

では、dV/dtが大きい(変化の早い/高い周波数成分を含む)パルス状のノイズはどういった時に起こるのでしょうか?これは当ホームページの“32. 物理屋が出番?ESDガンの特性はやっぱり物理的”で説明しましたが、火花放電が生じる前後(グロー放電の発生)で起こります。但し、定負荷下で規定されたESDガンのパルス波形を使って被試験機の任意のフレーム部位にESDガンを接触させて試験を行うのですが、その接触部での負荷インピーダンスは前述の定負荷とは全く異なる負荷条件となるため、規定通りのパルス波形をそのまま被試験機側に印加することはできず、特にパルスの高周波成分は入力されなくなります。

しかし、ESDガンによる被試験機に対する気中放電や、ESDガンでの接触放電でも被試験機内で2次的な火花放電を生じた場合は、その火花放電により試験機内の回路基板のGND電極と各ラインとの間でより大きいdV/dtをもつパルス状のノイズが生じているのではないかと考えております。

このdV/dtを如何に小さくするかですが、当社がご紹介しております“PD適用実践編”、“SD適用実践編”で説明している方法もdV/dtを抑制する方向に機能します。しかしそれ以上に、ESDガン印加後の2次放電の発生抑止が重要なESD対策と考えております。詳細は“IEC61000-4-2試験対策 Part-II ”のセミナーの中で説明しております。

※関連ページ

32. 物理屋が出番?ESDガンの特性はやっぱり物理的

ESDサージ・雷サージ・・・何が起きているのか、ご存知?

サージ関連試験での不具合対策は試験パルス印加による2次放電発生も勘案して

27. ESD試験時の2次放電発生の予見をsimで確認・・・これが不具合原因!

ESDシミュレーションに新たなソルバー登場!

ESD試験(IEC61000-4-2)対策に関する技術資料

32. ESD対策、物理屋が出番?ESDガンの特性はやっぱり物理的!

電気回路の中でコンデンサは交流電流を流す素子として扱われますが、その素子の中でどのような動作で電流が流れているのか、までいちいち考えながら扱っている方はいないでしょう。コンデンサは誘電体を2つの電極で挟んだ単純な構造ですが、その電極間では電荷(電子)が誘電体の中を移動して電極間の電流を流すということではなく、電極間の電場の変化(交流電場)によって2つの電極にそれぞれ異なる極性の電荷を溜め、次の瞬間にその電荷を送り出すといった動作を繰り返すことで交流電流が流れます。

但し、この時交流電圧Eが掛かるタイミングとそれによる交流電流Iのタイミングにズレが生じます。その時の状態はオームの法則で表すことができ、I = jωC・Eとなり、jは虚数で交流周期の1/4(複素平面で90度)を表しますから、交流電流Iは印加される交流電圧Eよりも交流周期で1/4周期早いタイミングで流れることを表します。このような電流の流れ方を変位電流(電束電流)と言います。

ここで、前述したコンデンサの誘電体を空間とした場合を考えます。2つの電極が対向した所謂空気コンデンサの形態となりますので、2つの電極間に交流電圧が印加されれば、変位電流が流れます。この変位電流は、交流の様な周期的な交番電圧でなくても静電気放電のような瞬間的な電圧変化であっても流れます。そのため、電極が対向した空間で電極間の電圧がパッシェンの法則を満たす電圧に達するまでは変位電流が流れますが、パッシェンの法則を満たす電位差になると電極間には火花放電が発生し、今度は電子による実電流が流れます。この時電子が空間を自由飛行するとイメージされる方もいますが、通常の空気の空間の場合は空気を構成する気体がイオン化(プラズマ化)することにより、そのイオン間の電子の授受を介して電子伝導が行われます。そのため、流れる電流量は変位電流の時に比べ千倍以上の電流となって流れます。また、火花放電が起きるときは一般的にはグロー放電が起き、その後更に十分な電力が供給されるとアーク放電に移行します。アーク放電の特徴は定電流特性です。

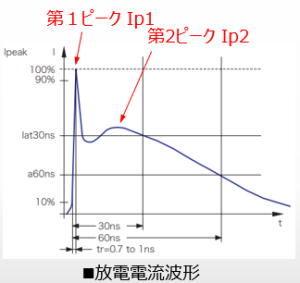

このことを踏まえてIEC-16000-4-2で示される放電ガンの電流特性のグラフを観ますと、第2ピークの時間帯は電流変化が比較的小さくなっており、極めて短時間に電力が注入されることによるアーク放電ではないかと思われます。アーク放電は電力の供給が低下し且つ、アーク(陽光柱)が立っている周囲の温度が低下すると消滅します。これに対し、第1ピークの瞬間の前半は電極間の電位差の上昇と共に放電路となる領域の気体のイオン化が進行したストリーマと言われる状態となり、発光が無い(発光する場合もあります)ものの電子伝導ができる状態となります。第1ピークの瞬間の後半はグロー放電として発光を伴う火花放電を生じると共に、電極間の電位差が急激に低下し、電子伝導による電流量も急激に低下していきます。よって、電極間に変位電流が流れるのは電極間に電位変化が生じた最初の極短時間(0.1~0.3nsレベル)だけではないかと考えられます。

ESD関連の記事ではESDガンによるESDパルスの印加後、変位電流や磁気的誘導電流によりスペースのある導体パターン間であってもESDパルスは流れ込んでいく状況を電磁界シミュレーション等の表面電流の可視化から説明されたりしますが、実は先に説明したようにESD印加時は通常の電気回路学や電磁気学とは異なるダイナミックな物理的反応によって電圧及び電流の分布が変化するため、通常の電磁界シミュレーションで解析するのは困難なのです。詳細につきましては“27. ESD試験時の2次放電発生の予見をsimで確認・・・これが不具合原因!”をご覧ください。

しかし、電磁界シミュレーションによって火花放電前はどのような状況なのか、また火花放電を起こしやすい部位等があるのか、等を可視化することは可能です。当ホームページの記事“サージ関連試験での不具合対策は試験パルス印加による2次放電発生も勘案して”にもある様に、当方はESDガン印加後の2次放電の発生を重要視しており、その発生抑止が重要なESD対策と考えております。詳細は“ESD試験(IEC61000-4-2)対策に関する技術資料”をご参照ください。また、火花放電発生と機器の不具合発生との因果関係についてはまた別の記事でご紹介したいと考えております。

※関連ページ

サージ関連試験での不具合対策は試験パルス印加による2次放電発生も勘案して

27. ESD試験時の2次放電発生の予見をsimで確認・・・これが不具合原因!

ESDシミュレーションに新たなソルバー登場!

ESD試験(IEC61000-4-2)対策に関する技術資料

31. 電源・信号ラインに対向するGND電極の幅は広い程よい、って本当?

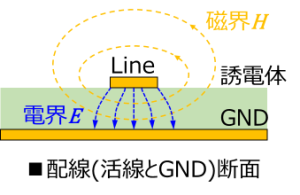

EMC関連のセミナーを聴講させて頂くと、よく講師の方が下図のようなマイクロストリップ線路のモデルを示して、電源ラインや信号ラインの形態で活線に対向するGND電極パターンで活線(ライン)方向に対する幅方向の長さ(幅)は広い程よい、という説明をよくされます。

理由として、

①GND電極パターンにより生じるインダクタンス成分を逓減できることにより、

②GND電極パターン全体の電位を0Vに近づけることができ、

③GND電極パターンにより生じる不要輻射(EMI)を低減できるから、

等と解釈しているようです。

一般的なEMCを担当されている方々は、素直に納得してしまうかもしれません。でも、これって本当なのか、と疑ってみるのも自身のスキルを高めるために必要かもしれません。

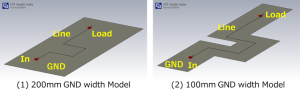

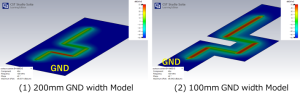

そこで電磁界Simを使って伝送路に於ける電流・電圧分布の状況を可視化してみました。伝送路のモデルとして屈曲部を持つ長さ300mmのマイクロストリップライン(伝送路)を活線側の幅を0.2mm、GND側を(1) 幅200mmのベタパターンと、(2)幅100mmで活線側に合わせて切り欠きのあるパターンとして、それぞれのモデルの誘電体厚みを0.1mm(4層基板の表面層を想定、下図参照。)としてSim計算してみました。

下図は100MHzでの(1),(2)モデルのGND電極に於ける電流分布を示しています。(1),(2)モデル共にGND電極上で活線と垂直に対向した領域に電流が分布した状態となっており、(1),(2)モデル共GND電極の幅方向の端部の電流分布は殆ど0に近い状態となっています。

ここで先ず、確認しておきたいことは電流分布があるということは電位(電圧)があるということであり、電流分布が無いということは電位が0Vということになります。即ち、電流は電荷の移動であり、電荷があるということは電圧を持つことを意味するからです。従いまして、AC(高周波)であれDC(ACの周波数を0に近づけていってもその途中に特異な特性上の変化点は無い)であれ、活線と対向するGND電極の領域には電圧(活線に対して反対極性)が生じ、その他の領域で電位は0Vに近づきます。

ということで、上記②で述べたGND電極パターン全体を0Vに近づける、というのは現実とは異なる考え方なのです。そもそも活線側に信号(高周波)や電源の電圧がかかっているのにその対向側が常に0Vという考え方は電気回路学のような伝送路の長さ・形状を考慮しない回路モデルの考え方であって、その考え方をそのまま現実の回路に当てはめるのは適切ではないのです。

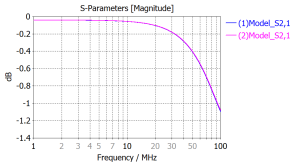

また、前述の①に述べたGND電極のインダクタンス成分に関しては、(1)、(2)のシミュレーション結果から(2)の伝送路の伝送路インピーダンスが大きくなる傾向になっており、GND電極の形状による伝送路インピーダンスへの影響はあると考えられます。しかし重要なことは活線とGND電極が常に対向した形態で伝送路において連続し且つ維持された状態となっていることで、(1)、(2)のシミュレーションでの伝送路における各周波数での損失は下図に示すように略同等となっています。

更に、前述③に述べた不要輻射(EMI)関係は伝送路の形態(活線やGNDの各パターン)や寸法、更には信号(ノイズ)の周波数に依存するため、今回のモデルだけから結論を出すことは難しく、場合に合わせて検討すべき、となります。

但し、GND電極パターンを広くしたから不要輻射が低減するというのは、少しステレオタイプ的で、やはり対向する活線側のパターン形状も考慮すべきです。活線側のパターン形状で共振(定在波)が起きている状況では、GND側でも同時に共振(定在波)を起こしていることを意味し、GND電極パターンを広くしたから共振が起きないということにはならないのです。

こう言った信号ライン、電源ラインにおける共振抑制には当社のSD適用、PD適用といった考え方を是非ご検討して頂きたいです。これらはシミュレーションで行いますので、ノイズ抑制効果(ノイズ輻射量の数値化は不可)を数値で検討できますし、素子の調整も可能でEMC設計として回路図設計段階での検討が可能となります。

EMC関連のハウツー本等の中で著者のイメージからGND電極パターンについて解説している記事もあったりしますが、Simをしてみるとその思い込みのイメージとは異なっていることが分かります。当社は“EMC設計 MBDでDX! 技術&学術”の セミナーでGND電極について解説しております。こちらも是非ご検討下さい。

少し話題がズレますが、活線とGNDとはそれぞれ異なる方向に電流が流れるという考え方から、活線とGND間には所謂“フレミング左手の法則の力”による斥力が生じていると考えている方も居られるようですが、前述したように活線とGNDには異なる極性の電荷が移動することからそれらの電荷による“クーロンの法則の力”(引力)が働くので、先ほどの斥力はキャンセルされるとも言えるのです。理屈っぽい話になりましたが、結局のところ、実際の活線とGNDの間には引力も斥力も存在しません。

※関連ページ

PD適用に関する技術資料

SD適用に関する技術資料

EMC設計 MBDでDX! 技術&学術

30. 基板端部配置のコネクタ周辺、如何なるノイズ対策が有効か?

回路基板のA/W設計を行っている時に、回路図面の信号ラインや電源ラインが回路基板端部よりコネクタを介して他の回路基板に繋がる構成となっていて、その信号ラインや電源ラインにEMC対策のフィルタを挿入する設計になっているような場合に、そのフィルタの配置に関して、①各ラインの信号源又は電源側、或いは②各ラインそれぞれのコネクタ側の何れがよりEMC設計として好ましいでしょうか?

これに関してはケースバイケースな面もありますが、EMC設計の段階としては迷わず①を考えるべきです。フィルタの類は基本的に伝送線路におけるインピーダンスミスマッチによって不要帯域のノイズをノイズ源側へ反射させる機能を持ちますので、不要なノイズをできるだけノイズ源から漏洩させないようにすると考えるべきでしょう。しかし、ケーブル等からのノイズの輻射を想定すると、ケーブルが接続するコネクタ部の方がより効果的にノイズ抑制ができるのでは、とも考えられます。しかし、既にケーブルに接続先の他の回路基板からのノイズが重畳してきている場合には、そのノイズに対してコネクタ付近に配置したフィルタはそのノイズをケーブル側に反射させてしまうので、ケーブルにおけるノイズの定在波を起こしやすくなり、ノイズ輻射の原因となってしまいます。やはり、フィルタの類のコネクタ付近の配置はあまり好ましいと言えません。

同軸ケーブル等伝送インピーダンスが調整されたケーブル等を除くと、よく使われている回路基板間を接続するケーブルのインピーダンスは高め(100Ωを越える程度でしょうか?)で且つ一定ではありません。それに対し、4層基板等の回路基板のラインのインピーダンスは70Ω以下程度と、よく使われる(廉価な)ケーブルに比べ低めになります。そのためどうしてもコネクタ部ではインピーダンスミスマッチが生じ、ノイズとなる周波数帯域では定在波が生じやすくなります。

ただ、この時の特徴としてコネクタ部での低いインピーダンス側となる回路基板側の伝送路で生じる定在波の電流振幅は増大する傾向となります。そのため、その増大した電流振幅を逓減させる損失系の素子(抵抗やビーズ)をコネクタ付近で挿入させることはノイズ低減する上で極めて有効となります。

しかし、実際の回路基板の実装の状況をみると、コネクタ周囲にはコンデンサが数多く配置されている例が多く、回路の考え方は様々と思いながらも私としてはどの程度有効に機能しているのか、等と思ったりします。

こう言った信号ライン、電源ラインにおけるフィルタの類やビーズ、コンデンサ、抵抗といった素子の機能及びノイズ抑制効果、更には回路を機能させるための信号品質の検討に当社のSD適用、PD適用といった考え方を是非ご検討して頂きたいです。シミュレーションで検討しますので、ノイズ抑制効果(ノイズ輻射量の数値化は不可)を数値で検討できますし、素子の調整も可能で設計段階でのEMC設計上での最適化も可能です。

※関連ページ

PD適用に関する技術資料

SD適用に関する技術資料

2. ICの電源ライン、パスコン最適化に当社のPD適用。

3. 信号ラインのダンピング抵抗、当社のSD適用のSimモデルで抵抗値を設定。

10. EMC設計、レガシー3D-SimからMBD (1D-CAE)へDX!

23. 回路基板のデジアナ分離・・・GNDパターンは、、、

MBD、EMC設計を革新

DX時代のイノベーション

29. A/W設計における電源配線ルール。“跨ぎ”とか“島状配線/スター形配線”、注意が必要かも!

当社ホームページの記事、“5. 回路基板におけるEMC設計の実践と検図。当社のWDを提案。”というのがあり、その中で

~例えば、回路基板設計におけるEMC設計の有名なルールとして信号ラインの”GND跨ぎ禁止”、”電源跨ぎ禁止”があります。このルールを守れないとEMCルールチェッカーでは”跨ぎ”を生じている箇所を指示してEMCリスク”高”を警告します。しかし、4層基板などでは、通常2層目をGND層、3層目を電源層とするので、4層目の長い信号ラインは必ず”GND跨ぎ”や”電源跨ぎ”が生じます。もし、このルールを回避出来なければ、4層基板を試作してはいけないのでしょうか?~

と記載しております。

4層基板については、基本構成“1層目(表面/A面)・配線層、2層目・ベタGND層、3層目・電源層、4層目(裏面/B面)・配線層”としていることを前提としています。

この構成で必ず生じる4層目の長い信号ラインの”GND跨ぎ”や”電源跨ぎ”は、是非当社が提案しております、WDのA/Wのルールを適用して頂ければEMIの課題を回避することができます。是非当社のWD Part-II<A/W設計ルール>を参考にして頂きたいです。

今回は、特に3層目の電源層のパターニングについて考えてみたいと思います。

一般的に機器の回路基板の電源配線については、回路基板上の電源部位から機器の回路のコアとなるSOCや複数のドライバーICの各電源端子に向けて、“できるだけ距離を短く”、且つ“できるだけ配線パターン幅を広く”して配線すべきと先ず考えるでしょう。またハウツー本や業界誌等でもそう指導したりしています。その意図するところは、電源配線パターンの導体損失(IRドロップ)を低減することと、電源配線のインピーダンスをより低くするためです。

そのため電源配線パターンとしては、回路基板上でSOCや各ICが配置される領域を含むように大きな矩形パターンを配置して、そのパターンからSOCや各ICの電源端子にVia等を介し結線して低インピーダンスで低損失な電源配線パターンを形成するでしょう。また、この構成により大きな電源パターンが2層目のベタGND層と対向して接地コンデンサ的な形態になるので、電源ノイズを低減させる効果が期待できると考える方も居られるでしょう。この配線の仕方は島状配線と呼ばれることもあり、よく行われている電源配線方法です。

しかしながら島状配線に関しては、そのパターン形状によりEMIノイズの要因とされる形状共振が生じ易いという指摘もあり、その共振現象を回避するためにSOCや各ICの電源端子にそれぞれライン状パターンで直接向かわせる電源パターンとする考え方もあります。これについてはスター型配線とも呼ばれたりします。

電源配線に関してはEMC設計の観点から、回路基板上(更にはケーブル等で接続される子基板上も含めた)SOCや各ICの電源端子と、電源部位との間の高周波帯域でのデカップリング(非結合)が十分とれているかが重要となります。このデカップリングの評価について、当社はPD適用をご紹介しております。詳細につきましては、“PD適用・基礎編”、“PD適用・実践編”を是非ご参考にして頂きたいです。

このPDで評価すると、ICのクロック周波数の高調波帯がEMIの対象帯域となる場合は30dB以上、クロック周波数の基本波がEMIの対象帯域内となる場合は50dB以上のデカップリングが必要となります。こういったデカップリングを得る上で、電源配線の島状配線は不利な形態になり易いのです。

電源配線で、IRドロップを最優先課題として配線設計しがちかもしれませんが、EMC設計の観点からの事前の評価も是非ご検討頂きたいと考えております。PDの評価からは、電源ラインのインピーダンスは高め、ライン長としては長め、にすることにより電源デカップリングは増大させ易くなります。しかし、電源配線のIRドロップ対策に対しては相反する形態となります。従って、必要とするデカップリングを得られるように配線幅・長さを予め設計しておく必要があります。その設計に際してはシミュレータを使ったPDで評価しておくことをお勧めします。

また、この電源デカップリングの考え方は、当ホームページの“23. 回路基板のデジアナ分離・・・GNDパターンは、、、”でも記しておりますが、デジアナ分離にも適用できます。分離の状況についてPDを使って評価することができます。

※関連ページ

2. ICの電源ライン、パスコン最適化に当社のPD適用。

5.回路基板におけるEMC設計の実践と検図。当社のWDを提案。

23. 回路基板のデジアナ分離・・・GNDパターンは、、、

PD適用に関する技術資料(PD適用・基礎編/PD適用・実践編)

電源ライン設計を革新。PD適用

WD Part-II<A/W設計ルール>

28. EMCフェライトコア、機器・装置のフレームグランド(GND)に嵌める!

不要輻射(EMI)対策の現場で、何となく機器・装置等のフレームグランドがアンテナとなってノイズを放出しているのではないか、等と考えてしまうことはないでしょうか?そんな時、フレームグランドにフェライトコアを嵌められないだろうか、なんて思ってしまうことはないでしょうか?対策活動が苦しくなってくるといろいろ妄想してしまうものです。

当ホームページの“24. フレームグラウンドにノイズ電流ッ!、、、普通に流れます。”でも記しておりますが、フレームグラウンドにノイズ電流が流れ、それがノイズの不要輻射(EMI)の要因になることは明らかであり、その状況は電磁界Simでも確認することができます。

EMI対策を検討している機器・装置の内部のエレキ構成にもよりますが、もしメイン基板とサブ基板があり、それらをハーネス(ケーブル)で接続する構成がある場合、大概そのハーネスにフェライトコアを装着してEMI対策の効果を得ていることでしょう。そこで更なる効果を期待して上記したような“フレームグランドへのフェライトコアの装着を妄想してしまうのかもしれません。

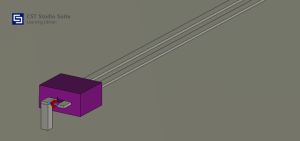

このフェライトコアに関しては当ホームページ“EMCノイズ対策部品のフェライトコア。EMI対策の定石?”の中でも触れていますが、そのEMI低減のメカニズムについて、電磁界シミュレータ(CST Studio Suite LE)を使って検証してみました。

図-1

図-1はSim検証するためのモデルであり、信号ラインとGNDラインの対でハーネスを想定したモデルとし、そのハーネスモデルの下方にベタのGNDパターンを配置してこれでフレームを想定したモデルとして、同一フレーム内でメイン基板からサブ基板に信号を伝送している構成をSimモデルとしてみました。

ハーネスのGNDラインは下方のベタのGNDパターンと接続しており、信号ラインとGNDライン対の一方の端に信号源、他方は開放の状態にして、信号ラインとGNDラインの対の信号源側の近傍にフェライトコアを装着(コアの中央の隙間にハーネスを通す)した状態にしています。

図-2

図-3

図-2は信号入力後0.9ns後のSim結果であり、図-3は上記のフェライトコアをハーネスに装着しなかった時の信号入力後0.9ns後のSim結果です。図-2、図-3を比較して観ると、フェライトコアの有り/無しにより、ライン対(ハーネス)の下方のベタGND、即ちフレームでの電流値及びその分布はフェライトコアが有る時の方が小さくなっていることが分かります。

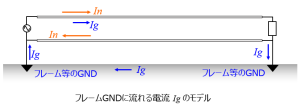

このメカニズムは当社のホームページ“24. フレームグラウンドにノイズ電流ッ!、、、普通に流れます。”でも説明していますが、図-4に示すように、信号ライン対又は電源ライン対の活線側及び、フレームGND(図-2、3ではベタGND)を流れる電流Igに対してフェライトコアがインダクタとしてチョーク(電流を抑制)しているためなのです。

図-4

従って、電流Igをチョークする作用として“フェライトコアをハーネスに装着した”というのは、“フェライトコアをフレームグランに履かせた”と同等ということになります。何れによっても電流Igはチョークされ、機器・装置のフレームがアンテナ(放射体)となって放出されるノイズは低減されます。

しかしながら、不要輻射対策の現場で、既にハーネスにフェライトコアを装着しているのに、ノイズレベルが規定値まで下がらず、フェライトコアをハーネスに数珠の様に複数装着させている状況もあったりします。ご存じのようにフェライトコアの装着は1個目で顕著なノイズ抑制効果を発揮しますが、更にコアを追加しても期待したノイズ低減効果は得られないものです。これは基本的に信号ラインや電源ラインにおけるノイズレベル(絶対値)が高いためなのです。

そのような時は、当社が提案しております、PD、SD適用でノイズ対策を施し、更にノイズ抑制効果を追加したい場合にフェライトコアの装着を加えることをお勧めします。尚、PD、SD適用は回路図設計段階から実施できるEMC設計です。

関連ページ

24. フレームグラウンドにノイズ電流ッ!、、、普通に流れます。

25. これがグラウンド(GND)を流れるリターン電流!

EMCノイズ対策部品のフェライトコア。EMI対策の定石?

EMC設計 MBDでDX! 技術&学術

信号ラインのEMC設計は”SD適用”で決まり!

電源ライン設計を革新。PD適用

27. ESD試験時の2次放電発生の予見をsimで確認・・・これが不具合原因!

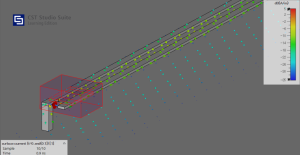

当ホームページのコンサルブログの記事、“サージ関連試験での不具合対策は試験パルス印加による2次放電発生も勘案して”や“ESD試験(IEC61000-4-2)対策に関する技術資料”のテキストPart-Iの中で2次的放電に関する下記図-1等で解説しておりますが、ESDガンの印加による機器内での2次放電発生の可能性について電磁界Sim(CST Studio Suite LE)を使って検討してみました。

図-1

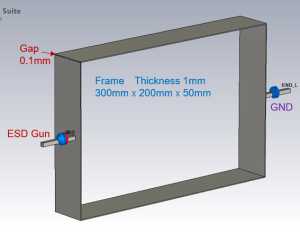

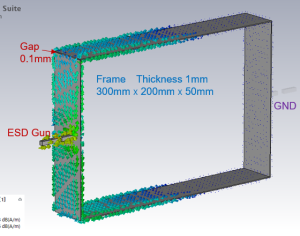

そのSimモデルは図-2に示すように厚み1mm、幅50mmの金属板を周回させてフレーム(300✕200✕50mm)とし、その周回の起点と終点となる部位に0.1mmのギャップ(空隙)を作っておきます。これは一般的な電子機器の金属フレームを想定し、その金属フレームの一部に電気的な接触が不十分な状態(接触する金属板間での溶接不良とか金属表面上の防錆メッキの酸化による不導通化等)が生じた状況を想定しています。

図-2

この金属フレームに図-2に示す箇所に機器をアースするGND配線を設定し、ESDガンよりESDパルス(基本的にはIEC61000-4-2 で規定された電流パルス)を注入します。ESDガンの設定電圧は4kV(ESD耐性を観るための高めな設定)としています。

図-3はESDガンからのESDパルス注入後1.1ns(所謂ESDパルスの第1ピークの時間帯)におけるフレーム表面上のESD電流の流れる状況を示しています。ESD電流の流れ方の特徴としては、ESDガンの電圧印加時の放電チップの極性によりますが、放電チップ側からフレームのGND端子側に向けて(或いはその逆に)電流は流れていきます。その際、電流は金属フレームのエッジ(縁部)に集中して流れていく傾向があります。これは電流とそれによる磁界成分との関係で、フレームのエッジ周辺の空間で磁界成分が急激な方向転換(⇄のような)を生じるため磁界密度が上昇し、それを補う電流密度の上昇が生じるため、と考えられます。勿論その状況はこのSimでも確認できます。

図-3

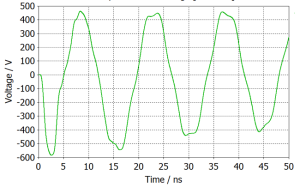

このESDパルスが印加された際の上記の0.1mmのギャップに生じる電圧について、図-4に示します。このSimの結果によると、ギャップ間にはESDパルスの印加後50nsの間に7回にわたり300Vを超す電位差が生じていることが分かります。ここで、0.1mmのギャップに300V以上の電位差がかかった時、何が起こるかが問題なのです。