グランドノイズと聞いて、どんなイメージを持たれるでしょうか?

機器のグランド(アース)電極を介して機器の様々なところへ流れ込んで、予期せぬ場所から空間に出ていくのでは、、、等と考えて、EMC対策としてグランドノイズは低減すべきもの、と考えておられる方もいるでしょう。

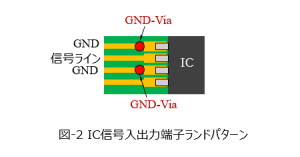

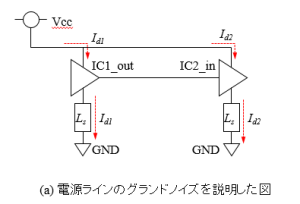

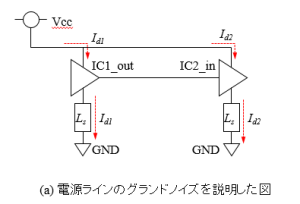

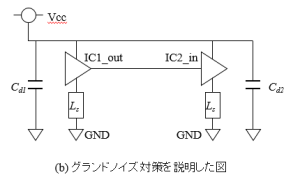

グランドノイズに関してはEMC関連のハウツー本やWEB等でよく解説されています。ここで簡単に説明しますと図(a)に示すようにICが電源ラインとGND電極に接続する際、IC内の特に出力バッファーの動作(Lowレベル⇔Highレベルの遷移)において瞬間的に電源(Vcc)側からGND側へ貫通電流が流れます。この時、IC内のバッファーと回路基板上のGND電極の間に介在する寄生インダクタンス(Ls)により電圧が発生し、これがグランドノイズとなります。

正確には、電源(Vcc)側の配線においても寄生インダクタンスが存在しますので、その寄生インダクタンスも含めてグランドノイズとされている方もいます。また、Vcc側の電源配線を介してIC外部に漏洩していくイメージから、電源ノイズとしている方もいます。当方としましては、ノイズであっても活線とGNDの2極により伝導する電源ラインのノイズと考えています。

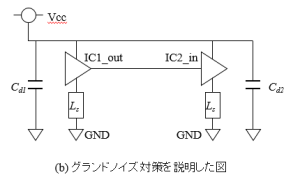

さて、このノイズの対策としては図(b)に示すようにパスコンCd(デカップリングコンデンサ)を用います。パスコンCdにより、VccとGND間の交流(高周波)電位を0V(交流短絡)にすることにより寄生インダクタンスLsによるノイズ電圧の発生を抑制させます。しかし、実際のパスコンCdには寄生インダクタンスがあることや、パスコンとIC内バッファーとの間の接続においてインダクタンス成分があったりすることで、前述の交流短絡の効果が低下します。その対策として、パスコンに寄生インダクタンスの低減を目的としたLW逆転型や三端子型といった特殊なパスコンを適用させたり、ICとパスコンの間の配線に伴うインダクタンスを低減するICパッケージやパスコンの実装方法を適用させたりといった多くの方法があります。

一般的に、低クロックのCMOS ICであれば、電源パスコンを必要とするものの、あまり前述のような寄生インダクタンスを気にする必要はなく、即ちグランドノイズの発生を考慮する必要はありません。しかし、高クロックのCMOS ICとなると上記のような特殊なパスコンを検討する必要が出てくる場合もあります。

ただ、押さえておくべき点として、パスコンの実装によりパスコンの接続した点でのノイズ(高周波)帯域で十分に交流短絡(電気回路的には0Vとなることは無いので電圧値としては-40dBV (=0.01V) 以下と言った値を目指すことになります)ができているか、と言うことです。

PIの通常の評価では指標としてICの電源端子側からみた電源側のインピーダンス(インプットインピーダンス)をICが安定動作する(とされる?)ターゲットインピーダンスよりも低くなるようにパスコンの選択と個数の調整等を行います。実際の現場ではターゲットインピーダンスが分からないことが多くインプットインピーダンスをできるだけ低くして、それにより高周波のノイズ帯域で十分に0Vに近づくようにしています。

しかし、電源ラインの途中に回路基板間を接続するケーブルが介在する場合は、上述のPIでの評価では十分ではない場合があります。PIを検討できる市販のツールでは複数の回路基板及びそれらを接続するケーブルからなる電源系におけるPIの評価を対象とはしていないからです。実際のEMI対策の経験を通して、電源系のEMI(不要輻射)ではケーブル起因によって生じている場合が多いのです。

当社のPDは電源ケーブルを含んで電源系のノイズを評価することができます。詳細説明は”PD適用・実践編”でご紹介しますが、回路図の段階で電源ラインにおけるEMI設計のために取るべき対策及び検討方法(シミュレーション)について解説します。

ここで簡単にグランドノイズに関してまとめますと

①グランドノイズとはICの電源端子及びGND端子接続部に寄生するインダクタンスより生じる電圧ノイズです。

②グランドノイズはICに接続させる電源パスコン(デカップリングコンデンサ)により対策されています。

③パスコンの最適化設計はPI評価により行うことができます。

④但し、回路基板間をケーブルを介して電源供給が行われる場合は当社のPDを適用して電源ラインの設計を行うことを強くお勧めします。

※関連ページ

前節(11. 12. 13.)では電磁波の伝搬について説明してきましたが、空間を伝搬する際の減衰について触れていなかったので、当節で説明致します。

電界や磁界を高校時代の物理で習い始めると電界Eであれば距離rに対して、クーロンの法則から1/r2で減衰すると習った経験があるでしょう。これが所謂電界の空間減衰になります。磁界の場合も同様な関係で空間減衰します。

電磁波も伝搬距離rにより電磁波(電波)の振幅(即ち電力)が減衰していきます。但し、その減衰の仕方については、高校時代の物理では静電場・静磁場(直流場)であったのに対し、電磁波は動的な交流場となるため、その状況は多少変わります。

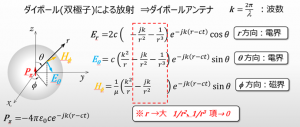

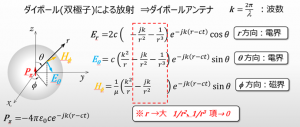

下記の図は動的な電気双極子(z軸方向のみで極性が入れ替わる)が空間に形成する電磁場について計算したものです。(導出プロセスは省略。詳細は電磁気学の書籍等で。)

この電気双極子により形成される電磁界は双極子の極性入れ替わり頻度(振動数)、即ち電磁波の周波数の影響を受けない理想的なダイポールアンテナにより形成される電磁界と同等になり、電気双極子の中央が信号源(波原・給電点)となります。

図において動径方向rが信号源からの電磁波の伝搬方向となり、動径方向rに対して横(垂直平面)方向がθ方向とΦ方向となります。式で記載された電界及び磁界で伝搬に伴う空間減衰について1/r、1/r2、1/r3の項があることに気づきます。rが極めて小さい場合は1/r < 1/r2<< 1/r3(各項係数省略)なる関係となり、rが十分大きな場合は1/r > 1/r2> 1/r3(各項係数省略)となります。特に1/rの項が支配的になっていく距離はr≈λ/(2π)(λは電気双極子の振動数(周波数)に対する空間波長)となり、このr < λ/(2π)の領域は近傍界、r > λ/(2π)の領域は遠方界としています。因みにλ/(2π)の距離(≈λ/6と考えてもよい)は例えば30MHzで160cm、100MHzで48cm程度になります。

遠方界はいわゆる電波の領域となり、1/rの項の電磁界(遠方界成分)となるので、動径方向r(伝搬方向)に電磁界は無く、伝搬方向に対して横方向に電界E及び磁界H を持ち、いわゆる波面を形成します。これらは前節で述べたTEM波の状況を式で説明しており、電界Eと磁界Hの積(E☓H)によるポインチングベクトルSが伝搬方向(動径方向r)に向かう状況も示しています。

一方、近傍界については少し複雑になります。特に信号源に近い側は電界において1/r3の項が極めて大きくなり、準静電界と呼ばれる領域になります。低周波であればあるほど大きな電界が得られる領域を確保できるため、その性質を利用した電子デバイスもあったりします。また1/r2の項が有効となる誘導電磁界とよばれる領域もあり、昨今は無接点電力伝送等で利用されたりしています。特にコンデンサ、コイルと言った部品の外界に形成する電界、磁界は近傍界であって、遠方界を持つことはありません。1/r2と1/r3の項は近傍界成分と言えるでしょう。

図にも示されていますが、1/r、1/r2、1/r3の各項はいずれも独立項で電界及び磁界はそれらの線形結合で示されるので、遠方界と近傍界は別のモノ(性質)であることを理解して頂けるでしょう。そのため、機器のEMI(不要輻射)の解析等で近傍界プローブを使ってマッピングを行ったり、電磁界Simで近傍電磁界を計算したりして、機器のEMIとの関係を探ったり、関連付けた資料を目にすることがありますが明確な関連付けは困難であり、結局想像力を駆使したイメージでの結びつけ程度のものにしかならないのです。

また、1/rの項の部分はアンテナの特性と関係するため、機器の基板・ハーネスなどは基本的にアンテナとしての能力は低く、電磁場の1/rの項に相当する部分は一般的には小さくなります。そうであるにも関わらず、近傍界プローブで測定した1/r2、1/r3の項のレベルを以って放射の原因であると結論づけたりすると、EMI対策として大きな遠回りをすることになったりします。

当節をEMC対策の観点でまとめますと

①放射する電磁波(ノイズ)は遠方界成分(1/rの項)です。

②機器の基板・ハーネスの周辺に関する電磁界Sim結果やプローブ測定結果は発生する電磁波(ノイズ)の近傍界成分です。

③遠方界成分と近傍界成分は別モノですので、近傍界の検討結果から遠方界を推測することは困難です。

私が高周波関係の仕事を始めた頃、先輩から”アンテナには近傍界があって電波がぐちゃぐちゃな状態から整った平面波に変化して遠方界で放射される”、と教えられて、それを信じて長く過ごしていました。その頃は遠方界での電波しか扱っていなかったので特に問題にはなりませんでしたが、EMCを扱う技術者の方々には考慮すべき事柄だと思います。

※関連ページ

本題の前2回の解説でノイズという電磁波について下記のようにまとめました。

①電磁波の電場Eと磁場Hは垂直の関係です。

②電場Eと磁場Hの一方が減少又は0になると伝搬する電磁波も減少又は0になります。

③電波はTEMモード(電波の伝搬方向に対して横方向に電場E 、磁場H )です。

④TEMモードの電磁波は電場Eと磁場Hのベクトル積となるポインチングベクトルSを持つ。

⑤ポインチングベクトルSが空間に向かうことで電磁波(ノイズ)は空間に放射されます。

⑥実際の機器ではケーブルのコネクター部でポインチングベクトルSは空間に向かう形態となっています。

⑦PD適用、SD適用はポインチングベクトルSのスカラー量を低減する回路的手法です。

今回は上記の事柄を踏まえて、回路基板上の配線を伝送する電磁波について触れ、上記の⑥について説明します。

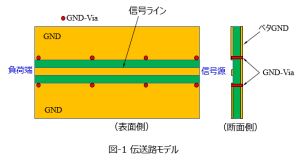

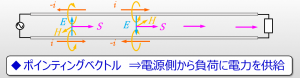

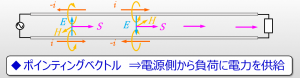

下に示す図は信号源(ノイズ源)から負荷に向かって回路基板上の配線を電磁波(ノイズ)が伝搬する状況を説明した図です。

先ず信号源はその電圧により信号源に繋がる配線の一方(Hot)の側導体に電流(i)を流出させます。この時、それと同時且つ同量の電流を信号源に繋がる他方(GND)の側導体より流入させます。電荷で説明すれば、信号源はHot側に電荷(+q)を供給し、GND側より同量の電荷を取り込む関係になります。この正電荷を取り込むという状態は、”信号源が負の電荷(-q)を供給する“、と物理的には同義になります。

よって信号源から同時に同量の電荷+qと-qが配線のHot側導体とGND側導体にそれぞれ供給されるので、Hot側導体とGND側導体の対向する空間で電荷+qから電荷-qに向かって電場E が形成されます。この電場E は電荷+qから出た電気力線のすべてが電荷-qに向かうため、divD = div εE = 0 となります。

また、配線に流れる電流についてみると、Hot側に電流iが流れる場合、GND側にも同量の電流が流れますが、その時、電流の流れる方向は反平行の関係になるため、Hot側の電流iに対してGND側は電流–i が流れることになります。前述の電荷の状況を考慮して配線を流れる電流を述べると、信号源からHot側導体とGND側導体に流れる電流は、一方に電流i、他方に電流-iがペアになって負荷側に向かって伝搬することになります。この電流のペアがそれぞれの導体に形成する磁場はHot側導体とGND側導体が対向する方向の面に対して垂直の方向に磁場Hを形成します。

このような電場Eと磁場Hが形成されるため、前回説明したように電場E、磁場Hにより形成されるポインチングベクトルSが形成され、Sは常に負荷側に向く形になります。将に、信号源の電力は負荷側に向かって伝搬していくことを示します。

図では、信号源が高周波(交流)であってもSは常に負荷側に向く状況を示しています。更に、ポインチングベクトルSはHot側導体とGND側導体が対向する空間内に保たれており、外界を向くことがないことも示しています。これは電磁界解析を使ったシミュレーションでも確認できますが、2本の導体(伝送インピーダンス一定)で信号源と負荷を繋げたモデルでは殆ど放射が起こらないことを意味します。

よって、4層基板等で第2層をGNDのベタパターンとして、そのGND上の第1層で長い配線や周回(ループ)状のパターニングを行ったとしても、その配線からノイズが放射されることは無いのです。但し、問題になるのは回路基板上の配線と外部のケーブルを接続するコネクター部でそれぞれの配線の断面形状が変化するために、配線の構成する導体間に保持されていたポインチングベクトルSが外部の空間に向く状況ができてしまうことがあります。この外界に向いたポインチングベクトルSが不要輻射(EMI)となります。

ポインチングベクトルSを外界に向けないように機器を設計するのは困難ではないものの、EMC対策コストを増大させるものとなり、そのコストは機器のユーザーにとって価値のあるものにはなりません。そこで上記の⑦で上げているように、当社が提唱しているPD、SDを使ってポインチングベクトルSのスカラー量を低減する回路的手法が適しています。EMC対策に対する費用対効果がよい上、回路シミュレーションを使うので機器の回路動作の事前確認にもなります。

是非、当社推奨のEMC設計、PD適用、SD適用をご検討下さい。

関連ページ

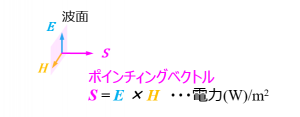

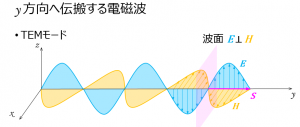

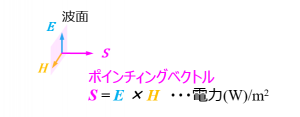

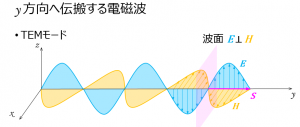

前回は電磁波についてその電場E 、磁場Hについて説明し、伝搬形態がTEMモードであると説明しました。このTEMモードであることをベクトルの関係で示すと下記の図のようになります。

即ち、電場Eに対して磁場Hが反時計周りで垂直の関係にあり、電場Eと磁場Hにより構成する面(波面となります)に対して垂直な方向が電磁波の伝搬する方向となり、ベクトル積E ×H = SとなるポインチングベクトルSを定義することができます。このポインチングベクトルは電磁波の伝搬する方向を示すと共に、そのスカラー量は電磁波の電力密度を示します。また、ポインチングベクトルSに対する電場Eと磁場Hによる電波の波面の特徴から空間を伝搬する電磁波を平面波と呼びます。そのため、もし励振源から電波が出ているとしたら、それは励振源から面的な広がり(風船が膨らむイメージ)で電波が放射されていることになります。更にTEMモードの電磁波は、下記の図のように一方向(y方向)に対して電場Eと磁場Hが垂直に交差すると共にそれぞれの強度もそれぞれ同一位置で互いに正の比例関係になります。その比例係数が空間インピーダンス(Z0≒120π (Ω))となります。

機器の不要輻射(EMI)を考える場合、EMC対策を担当される方々は”どうしてノイズ(電磁波)が放射されるのか?”という疑問を持つでしょう。そのメカニズムが分かればEMI対策のカギになることが期待できるからです。そこで上記の電磁波の説明は一つのヒントになります。即ち、ポインチングベクトルSが空間に向かっているかどうかということです。

その状況を観る方法として、アンテナにおける電磁界分布の状況を図等にしてイメージすると分かり易くなります。実は、”アンテナはポインチングベクトルSを空間に向ける装置である“ということを実感できるようになります。詳細な説明は当社のEMC設計 背景説明”4.機器からのノイズ放射のメカニズムを理解“のセミナーで行います。

実際の機器のEMIは、機器の基板とケーブルの接続部(コネクター部)がノイズ放射の励振部となり易い部位です。このメカニズムについては和田先生(京都大)のいくつかの論文の中で紹介されていますが(当方は和田モデルと呼んでいます。)、このコネクター部の信号ラインや電源ラインでポインチングベクトルSが空間を向く形態になっているのです。

当社が提供している、PD適用、SD適用はこういったポインチングベクトルSが空間に向く部位の回路の構成に一工夫を加えることで効果的にポインチングベクトルSのスカラー量を低減させ、即ちEMIを低減させる方法を提供します。その詳細についてはPD適用、SD適用の各セミナーの実践編で説明致します。

この辺で次なるEMC設計上で重要な点をまとめさせていただきますと、

④TEMモードの電磁波は電場Eと磁場Hのベクトル積となるポインチングベクトルSを持つ。

⑤ポインチングベクトルSが空間に向かうことで電磁波(ノイズ)は空間に放射されます。

⑥実際の機器ではケーブルのコネクター部でポインチングベクトルSは空間に向かう形態となっています。

⑦PD適用、SD適用はポインチングベクトルSのスカラー量を低減する回路的手法です。

是非、当社のセミナーを通してEMC設計の理解を深めて頂きたいです。

昨今のEMC対策セミナーで講師の方々は、ノイズは電磁波であるということを説明され、下記のMaxwellの方程式を示されて、電磁波の本質(?)であると説明します。

divD = ρ ・・・(1)

divB = 0 ・・・(2)

rotE = -∂B/∂t ・・・(3)

rotH = J +∂D/∂t ・・・(4)

∵B =μH, D =εE

セミナーの受講者で上記式を見せられた多くの人にとっては、何を言いたいのか全く理解できないでしょう。また電磁気学を習った経験がある人にとっても”だから何なの?”、と思うでしょう。

仮にEMC対策を担当されている方々がMaxwellの方程式をおぼえたとしてもそれを利用する場面はあまり無いでしょう。但し、電磁波の知識を深めるという点は期待できます。

ただ、下記の性質をMaxwellの方程式が示していることを理解して頂けると当社のEMC設計を深く理解する上で役立ちますので少し説明をしたいと思います。

その前に、先ず空間を伝搬する電磁波(電波)を考える上では、J =0であって、

rotH = ∂D/∂t ・・・(4*)

となります。当たり前ですが、電流が空間を流れることは無いからです。(回路基板上の配線を流れる電磁波(電流)を扱う際はJ ≠0となり式(4)の右辺を変形していきますが詳細は別の機会に)

また、式(1)についても

divD = 0 ・・・(1*)

とおくことになります。(1)の式でもρ = 0を含んでいると考えることもできますが、ρ = 0とρ ≠ 0には大きな差があります。

先ず、そもそも演算子divは、例えばベクトルAのある空間中でdivAを行うことで、その空間のあらゆる場所で、divAが正なら湧き出しが、divAが負なら吸い込みがあることを示します。これに対しdivA = 0ということは、ベクトルAは空間のあらゆる場所で湧き出し量と吸い込み量が等しいということになります。

ρ ≠ 0は静的電場(単一電荷が存在する状況で、所謂ESDを扱う条件下等)において成立し、物体が正又は負に帯電した際に張られる電場を示しています。しかし、電圧と電流により電力の入出力を行う、所謂直流・交流といった電気を扱う領域ではρ = 0となります。これは電荷が無いという意味ではなく、電圧と電流により対象とする電気の周囲の空間に張られる電場(E )は至る所で吸い込む電場(電気力線の数:電荷密度としては-ρ)と湧き出す電場(電気力線の数:電荷密度としては+ρ)が等しい状態になるためです。

磁場(H )に関してはご存知のようにN極から出た全ての磁力線がS極に至る性質があるので、周囲の空間は至る所で(吸い込む磁場)=(湧き出す磁場)の関係になり(2)の式となります。

よって上記のMaxwellの方程式は電磁波(直流から高周波)においては

divD = 0 ・・・(1*)

divB = 0 ・・・(2)

rotE = -∂B/∂t ・・・(3)

rotH =∂D/∂t ・・・(4*)

となります。

ここで気になるのがrotという演算子ですが、rotAは、ベクトルAの方向に対する垂直面内における回転ベクトルを示しますが、ベクトルAとベクトルrotAは垂直の関係だということが重要な点です。よって式(3)、(4*)から電場Eと磁場Hは垂直の関係であるということと、電場Eと磁場Hの一方が減少又は0になると、他方も減少又は0になり、即ち伝搬する電磁波は減少又は0になるということです。しかし、式(3)、(4*)からは時間微分された電束密度Dと磁束密度Bではないかと疑問を持たれる方もいるかもしれません。これは

D =D(r)・TD(t)= εE(r)・TD(t)

B =B(r)・TB(t)= μH(r)・TB(t)

とおいても(1*)~(4*)の式を満たすことができ、電場E 、磁場H の解とすることができるためです。よって、電場E 、磁場H のベクトル方向は時間の偏微分をしてもベクトル方向が変わることは無いのです。

(1*)~(4*)の式に対して、一方向(y方向)に進む電磁波(高周波のイメージで)の電場E 、磁場H について、ある条件を付けて解を求めると、

E=Ex・exp{2πj(y/λ-f・t) }

H=Hz・exp{2πj(y/λ-f・t) }

λ :電波の波長、f :電波の周波数

となります。この時のある条件とは、電波の伝搬方向(y方向)に対して電場E 、磁場H がベクトル成分を持たない(Ey = 0、Hy = 0 )という条件です。実はこの条件が空間を伝搬する電磁波(基板上の配線を伝搬する場合も含みます)の重要な性質となります。電波工学ではこのような電波の伝搬形態をTEMモード(電波の伝搬方向に対して横方向に電場E 、磁場Hがある)と呼び、電波を扱う上で重要な性質となります。尚、Ey = 0、Hy = 0ではない電磁波の伝搬モードも当然のことながら存在します。しかしEMCを対象とする場合は殆ど考慮する必要は無いのでこの場での説明は省略します。

今回は取りあえずこの辺で一旦EMC設計上重要な点をまとめさせていただきますと、

①電磁波の電場Eと磁場Hは垂直の関係です。

②電場Eと磁場Hの一方が減少又は0になると伝搬する電磁波も減少又は0になります。

③電波はTEMモード(電波の伝搬方向に対して横方向に電場E 、磁場H )です。

是非、心に留めておいて下さい。

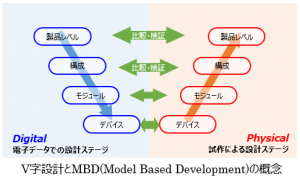

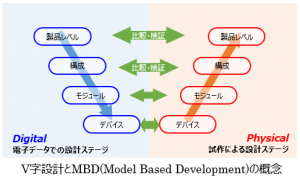

昨今のDX(デジタルトランスフォーメーション)のトレンドの中、各セットメーカー様の製品設計の現場においても設計プロセス上の課題を解決するために様々な検討がなされ、DX(狭義)となるような設計プロセスの改革(レガシーな考え方からの脱却)を検討されていることと思います。 幾つかの設計プロセスの中には製品のEMC課題もあるかもしれません。課題解決のためのEMC設計に関しては、既にEMC関連ツールのベンダー様より製品設計の電子データの段階(デジタル)でEMC設計を行うためのツールが市販されており、そのツールを導入し製品設計の段階で適用すればデジタルの段階でEMC設計ができる状況ができ、デジタル技術利用はもう実現できている様に見えます。 実際にそうなのでしょうか?少なくとも私が経験してきた製品設計の現場では全くそのような状況ではありませんでした。また、他のセットメーカー様のEMC関係者とお話をさせて頂いた中でも、製品設計の現場でEMC関係ツールの運用が上手く行っているといった話は一つもありませんでした。 展示会やセミナー等ではツールベンダー様やツールベンダー様と大手セットメーカー様の共同でいわゆるカッコよくEMC課題を解決した資料の提示を目にします。こんなに上手く行くのであればセットメーカー様の担当者は是非導入したいと考えるでしょう。しかし、”実際はそう簡単ではない”、という現実をここ10年間見てきたように思います。 また最近、あるメーカー様では20年以上電磁界系の3Dシミュレータを駆使してEMC設計の確立を目指してきものの結局実現できず、新たな試みとしてシミュレータメーカー側の協力を得て新たな電磁界系のシミュレーション技術を構築して新たなEMC設計の確立(デジタル設計革新)を目指す、といったことも聞いたこともありました。設計する製品レベルでの不要輻射(EMI)を新たな3Dシミュレーション(デジタル)で可視化して試作(フィジカル)前に問題を解決しておく、という将に理想の設計プロセスを実現するということです。 しかしながら、製品設計の現場で20年もの間、人とお金と時間をかけて実現できなかったことを、シミュレータメーカー側の協力を得ただけで実現できるものなのでしょうか?むしろ、20年かけて実現できなかったということは、やはり”そのやり方はよろしくない”という結論を示しているようにも思えます。 ここ10年、20年のEMC課題への取り組みは製品レベルや回路基板レベルへの3D-Simの検討・解析が中心でした。このレベルでのEMI等の検討は既にかなり複雑な構成になっており、そう簡単には解析できないことを多くの技術者が経験してきたものと思われます。私も過去約10年そのような解析をやってきましたが、やはりEMC設計の確立につなげることはできませんでした。やはり、3D-SimによるEMC設計は誰もが思いつくレガシーな考え方なのです。 また、製品設計のプロセスの進め方としても、仮に事前のSimの段階でEMIのリスク(可能性)に気づいたとしても設計プロセスの後戻りをしてまでの修正を施すかどうかの判断は難しく、製品設計を計画通り進めることが優先され、修正しないまま設計プロセスを進めるといった判断になるでしょう。 そこで考えられるのが、製品レベルや回路基板レベルといった完成に近いレベルでの検討ではなく、製品を構成する各要素のレベルで検討する方法です。EMC設計に当てはめるなら回路図レベルや部材(電子部品、ケーブル等、基板上の伝送路等)レベルから検討して製品レベルのEMIのリスクを低減させていく方法です。  この考え方は、昨今の自動車メーカーの開発プロセスとしてよく紹介されているV字設計とMBD (Model Based Development)による方法を適用したものです。製品開発において3D等の大規模な開発システム(ツール)を適用するのではなく、開発製品における開発すべき項目を、例えば構成→モジュール→デバイスのような各レベルで分解して各項目のレベルにおいて、1D-CAE(1次元的 : Computer-Aided Engineering)等を適用してモデルとして検討して、上位のモデルを実現できる下位のモデルを検討する方法であり、電子データで検証する段階をデジタル、試作による検証する段階をフィジカルと呼び、デジタルとフィジカルの結果を比較検討することにより、製品開発の高精度化・高品質化・低コスト化・スピードアップを実現するものです。 EMC設計においても、製品レベルや回路基板レベルでの3D-Simのレガシー的な適用ではなくモジュール・デバイスといったレベル、特に回路図設計段階から適用させていくべきです。Simのモデリングのためのデータインプット(Digitization)が容易で、Sim検討も関係技術者なら誰でも短時間にでき、且つ結果の共有(Digitalization)も可能で、MBDにおける上位のモデル構築にデータの紐づけとして利用することができます。例えば、回路図設計のレベルでノイズのエネルギーの低減化を検討しておけば、より上位のレベルのモデルにおいてもそのノイズのエネルギーが増大することは無いと言えます。 当社のEMC設計のアプローチは将にMBDであり、それを実現する方法としてPD、SD、WDを提案しております。上記の1D-CAEはSPICE系Simに当たります。この方法によれば、回路設計者であれば誰でもオペレーションが可能で、設計すべき事柄が明確です。また、費用的にも3Dの電磁界系Simツールに比べれば低く抑えられると共に、ライセンスの本数としても複数用意し易いです。更に、EMI低減効果は確実に出ます。(その状況は電磁界Sim等で確認することが可能)

この考え方は、昨今の自動車メーカーの開発プロセスとしてよく紹介されているV字設計とMBD (Model Based Development)による方法を適用したものです。製品開発において3D等の大規模な開発システム(ツール)を適用するのではなく、開発製品における開発すべき項目を、例えば構成→モジュール→デバイスのような各レベルで分解して各項目のレベルにおいて、1D-CAE(1次元的 : Computer-Aided Engineering)等を適用してモデルとして検討して、上位のモデルを実現できる下位のモデルを検討する方法であり、電子データで検証する段階をデジタル、試作による検証する段階をフィジカルと呼び、デジタルとフィジカルの結果を比較検討することにより、製品開発の高精度化・高品質化・低コスト化・スピードアップを実現するものです。 EMC設計においても、製品レベルや回路基板レベルでの3D-Simのレガシー的な適用ではなくモジュール・デバイスといったレベル、特に回路図設計段階から適用させていくべきです。Simのモデリングのためのデータインプット(Digitization)が容易で、Sim検討も関係技術者なら誰でも短時間にでき、且つ結果の共有(Digitalization)も可能で、MBDにおける上位のモデル構築にデータの紐づけとして利用することができます。例えば、回路図設計のレベルでノイズのエネルギーの低減化を検討しておけば、より上位のレベルのモデルにおいてもそのノイズのエネルギーが増大することは無いと言えます。 当社のEMC設計のアプローチは将にMBDであり、それを実現する方法としてPD、SD、WDを提案しております。上記の1D-CAEはSPICE系Simに当たります。この方法によれば、回路設計者であれば誰でもオペレーションが可能で、設計すべき事柄が明確です。また、費用的にも3Dの電磁界系Simツールに比べれば低く抑えられると共に、ライセンスの本数としても複数用意し易いです。更に、EMI低減効果は確実に出ます。(その状況は電磁界Sim等で確認することが可能)

難点としては、今までの設計プロセスの進め方に比べると多少の変更が加わることです。そもそも新しい考え方を現場の担当者に受け入れてもらうのは難しいものです。例えば、今まで回路Sim (SPICE)をやったことがない回路設計者には辛いことかもしれません。しかしSimが使えるようになることは他の開発・設計のシーンでも活用できる、といった自身のスキルアップのモチベーションをもって取り組んで頂けたら、と思っています。 それでも、MBDの考え方でのEMC設計の取り組みは、その導入時においてデジタル段階での時間的なロスが生じてしまうかもしれません。しかし試作(フィジカル)段階に至って、効果のあるEMIの低減を実現できます。 当社のEMC設計は、レガシーからの脱却なのです。

EMCの業界誌の文献やハウツー本を読んでいると、ノイズの原因としてのノイズ電流の流れ方をよく説明しています。シナリオとしては回路基板上の配線パターンにノイズ(高周波)電流が流れることにより、その電流の周囲に高周波磁場を作り、これが不要輻射の原因になるというイメージを付加したモデルで説明しています。そのモデルに関してはここでは触れませんが、配線パターンを流れる電流についてここで触れてみたいと思います。

前述の文献やハウツー本の中では電流について、正の電荷の移動としたり、負の電荷の移動として、その負の電荷は電子であると解説したりして、電気回路の入門者や物理学から電気回路を始めた人々を翻弄させます。中学生位に”電流は電池の正極から負極に流れる”と習い、高校の物理や化学を習うと、”電気は電子の移動”となり、電流は”正→負”なのか、”負→正”なのかチンプンカンプンの状態で電子機器の設計に関わっている方々も多いのではないかと思います。教科書を書かれるレベルの諸先生の中にも、物理学が十分に完成されていない状況下で電気の極性を決めてしまいその結果、電気伝導を担う電子の極性を負にせざるを得なかった、等と説明される方もおられます。確かにそういった側面もあるのかもしれません。

しかし、私の見方としては電子の極性はむしろ正しく、何の矛盾もなく電気回路-電磁気学-物理-量子力学-化学の各学術領域を関係づけていると考えています。そもそも各学術領域では、自然科学的な現象を説明するためにそれぞれの法則等に基づいたモデル(→方程式が立ち計算できる)で説明されます。例えば電気回路では電流を単位時間当たりの電荷量の流れと規定するので、電子をわざわざ持ち出す意味は無いのです。(コンデンサの帯電で正側の電極に+Q、負側の電極に-Qが帯電するので帯電電荷量は+2Qでは?と悩んだことはありませんか?これは電磁気学の考え方なのです。)

では電磁気学ではどうか?電磁気学でも電子を扱う必然性がありません。そもそも電磁気学で最初に習うのは電荷(クーロンの法則等)です。また電気回路に最も近い領域を扱う分野は”定常状態”という条件下での振る舞いです。そこでは電流の扱いもあり、divD = 0の条件下(詳細については別の場で説明します。)となり、簡単に説明すると、電源から負荷に向かう一対の配線に正の電荷と負の電荷(電荷の絶対量は等しい)が対になって移動していきます。正の電荷が負荷側に移動するのはイメージし易いと思いますが、同時に負の電荷が負荷側に移動している状況は多少イメージし辛いかもしれません。これについては、当社の”EMC設計 背景説明“で詳しく説明します。(この点が電磁気学ではコモンモード電流が存在しない理由になります。)

物理学(特に物性物理)の領域に至って電荷での説明では困難を生じるので電子(ドナーと呼ぶ場合もあります)を用いるようになります。これと対になるのが正の電荷を示す正孔(アクセプターと呼ぶ場合もあります)ですが、これは電子のような粒子ではなく電子が抜けたアナなのですが電子と同様な粒子性と波動性(量子力学的)を示し、これらは化学で言うところの電気伝導に関係するイオンや不対電子となります。これらにより物理と化学では電気の説明について矛盾なく結びつきます。

では電気回路との関係はどうでしょうか?単純な例として電池(直流)で作った回路で説明します。電池の負極から電池内部の化学反応により回路側に向かって電子が流れ出します。これと同時に電池内部の化学反応で流失した電子を補うために、電池の正極は回路側から電子の取り込みを行います。この状況をよくイメージしてください。電子(負の電荷)を電池の正極から取り込む(流出の逆)ということは結局、正の電荷を回路側に送り出しているのと等価であることに気づくでしょう。即ち、電気回路の領域では電源の正極から回路に向かって電流(正の電荷)が流れると考えることに何の問題もないことがわかるでしょう。

現象を説明するモデルがどういった学術領域からのものかを意識すると、変な横槍に対抗することができます。EMCの現象を説明するモデルについても同様です。電気回路の立場からか、電磁気学の立場からか、よく考えておきましょう。

関連ページ

通常EMC技術者は放射ノイズ(EMI)対策に関して、その3要素、”①ノイズ源”、”②伝送路”、”③アンテナ”を挙げるでしょう。故に、EMI対策の基本は”①ノイズ源のパワーを抑える”、”ノイズを②伝送路で遮断する”、” ③アンテナとなる筐体(フレーム)・ケーブルの形状をノイズ放射し難い形態にする”、といったことを検討します。しかし、①につては、IC内部の半導体のスイッチング特性(スルーレート)等によるものなので、セットメーカーの設計者としては調整の余地はありません。特に最新のICは半導体の微細化によってスルーレートが上昇し、動作クロックに関係なく不要輻射となるノイズのパワーは上昇しています。また③については設計する製品の外観・コンセプトにも関わる事になるので、EMI対策のためにフレーム(筐体)を変更するなどということは極めて難しいと思われます。そもそものEMI対策を考慮した製品のフレーム形状などというような設計要素を提案すること自体が困難です。

そこで、通常は②に注目してEMI対策するということになります。最もよく使われるのがEMC対策部品を伝送路上に付加するということになります。しかし、上手く行く場合もあれば、そうは行かない場合もあります。現場でEMI対策するEMC技術者は何とか担当する機器を次工程の設計・評価に送り出すためにあの手この手の調整を②に対して行い、何とかEMI対策を完遂していきます。本当に感心します。

ただ、こういったEMC技術者に対してもう少しノイズについて理解しておいて頂きたいことがあります。ごく当たり前のことなのですが、ノイズも電磁波であるということです。即ち、ノイズは空間を伝播する電波(電磁波)であると共に、回路基板上の配線においても電磁波であるということです。ノイズが電磁波であるということは、電磁気学的な振る舞いをするということと、電磁波であるので伝搬モードを持ち、波動性を持っているということです。これらを理解するためには、やはり専門的な知識の習得が必要となります。(専門的な知識よりも実践方法を熟知し、結果を出せればよいという考え方もあると思います。結果として課題が解決していれば問題はないのですから。)

前述の③アンテナについても電磁波の出入り口の中心となる給電点(Feed Point)の考え方が重要です。アンテナと言っても電波の送受信の機能を果たす装置としてのアンテナに比べて、ノイズを放射するアンテナ(機器のフレームやケーブルを素子(Element)とする)の電磁波放射性能は極めて低いのです。実はこの低さが機器のフレームやケーブルを多少変更してもEMI対策として効果が上がらない理由にもなっています。そのためアンテナの形状(素子)に目を向けるよりも給電点に注目することが重要になる訳です。

また、電磁波を検討していく上で近傍界と遠方界という放射源と受信点との間の距離における変化点があります。詳細については別の機会で説明しますが、EMIとして測定されるのは遠方界の電磁波であり、評価機器から距離3m或いは10mでの電界強度(dBμV/m)として評価されます。EMI対策に際して近傍界プローブによるスキャン解析を使うEMC技術者は特に近傍界と遠方界の違いをよく理解しておく必要があります。時としてそのような近傍界解析に費やす時間が無駄になる場合が出てくるためです。

ノイズは電磁波であることを理解して頂くことで、ノイズが如何に機器から放射されるかというメカニズムも理解できるようになります。これらの詳細については当社の”EMC設計・背景説明”の中でご説明致します。また、伝送路においてどのような対策をすればよいかを提案しているのが当社の”PD適用”や”SD適用”です。是非、ご検討頂きたいと思っております。

因みに、回路基板上の配線に関してEMC関連の文献やハウツー本で、配線長が長くなることによる配線のループアンテナ化に関する記載がよく見られます。確かに配線パターンの見た目からループコイルで磁界を放出するイメージを持っているのかもしれません。もし仮に、高周波帯(UHF帯以上)で使われるループ形状のアンテナ(ループ八木アンテナ)をイメージしているとしたら、そのループは磁界を検出する機能ではなく、電界を検出する機能としてのループ形状です。実際のループ八木アンテナは全エレメント(素子)を電波渡来方向に向けて、各ループの開口面を電波の電界と磁界の方向に対して平行の関係にしているので、磁界検出では無く、電界検出のエレメントとして機能します。

また、1ターンのループコイルをイメージしているとするなら、コイルの開口面を通過する磁界を検出するプローブと解釈することは可能です。しかし、プローブはアンテナと異なり、遠方界の電磁波を放出することはできません。これはコンデンサやコイルがアンテナにならないのと同じです。アンテナをよく理解されている方は、送信・受信は等価であるということをご存知でしょう。しかし、これはあくまでアンテナにおいて成り立ち、プローブでは成り立ちません。これらの詳細につきましては次の機会に解説したいと思います。

述べておきたいことは、回路基板に対する近傍界解析×ループ形状の配線→ノイズ放射、というようなイメージの結論からはEMI課題を解決できないどころか、大変な迷走の道に向かう危険性があるということです。

※関連ページ

EMC設計を解説する際、GND(グランド)は非常に重要なワードです。かつて私が見てきた現場のEMC担当者には、EMC評価にかけた機器の不要輻射(EMI)対策を行っている時などに、放射するノイズを何とか機器のGNDに落とし込むイメージを持って取り組んでいる担当者もいました。しかし、そのようなイメージに沿った方策で十分な効果が得られず、より効果の上がるノイズ対策の捻り出しに苦労する担当者もいました。

彼らは” GNDにノイズが流れ込んでいる”とか、”GNDパターン(電極)が揺れている”とか、あたかもノイズは流体のように流れ、GND電極の中へ流れ込ませるたり、流れ込んだノイズがGNDパターンの中で暴れたりする(共振のようなものか?)イメージを持っていたのでしょう。それ故か、GNDパターン内(電気回路的に電位差が無い領域)にコンデンサやビーズが入れられている回路的に奇異なEMI(?)対策した例を目にすることがありました。何とかEMI対策したいという思いから捻り出した方法だったのかもしれません。それでも彼らは何とか問題の解決策を見出して設計中の機器を次の設計段階へ送り出して行く姿は本当に凄いと思いました。

ただ、私としてはそんなEMC担当者にもっと役に立つGNDに対する情報や考え方を持てていれば、という思いがあります。

EMC担当者が機器のEMIの原因を考える上で当てはめるモデルは回路モデル(当社の一連の技術解説の中の”6. “で説明)です。この回路モデルにおいてGNDは大きさ・長さの概念は無く、且つ電位は0Vで、回路モデル内のノード(配線)でGND接続するノードは全て0Vになります。しかし、実際の機器のGNDは大きさ・長さを持っており、EMC担当者は実際の機器の状況と回路モデルの差を埋めるための調整・修正が必要と考えます。EMIの対策として”GND強化”と称してGNDパターンを大きく・太くするといった調整は代表的なものでしょう。

これは業界の文献やハウツー本等での、GNDによるEMI対策の説明の影響が大きいと思います。その説明では、先ず神様的な絶対0V となるシステムグランドを想定して、その絶対0Vが劣化(?)してしまうフレームグランド、更に0Vが劣化(?)してしまうシグナルグランド、等とGNDを分類します。実際の機器はその形状に伴うフレームのサイズや、機器のパワーケーブルの長さ、更に機器の回路基板におけるGND電極パターンの形状等、GNDと導通関係にある金属物はそれぞれがインダクタンス成分を持つので、ノイズとなる高周波電流がそれら金属物を流れるとそれら個々のインダクタンス成分により電圧を生じ、それがノイズ電圧となって放射されるとしています。(どういったメカニズムでノイズ放射するかは不明です。)そのため、回路基板の設計においては特に”配線パターンはできるだけ短くする”ということがよく言われます。配線パターンはノイズ電流の伝送路としても機能するので配線パターンのインダクタンス成分を低減させる、という考え方でしょうか。しかし、全ての配線パターンにそんなことができるわけはなく、いわゆる努力目標でしかありません。

また、EMIの要因とされる”グランドバウンス”というEMC関係者がよく使うワードがあります。これは回路基板内のGND電極上で生じる電圧変化であって、ICの動作時の急激な電流変化により生じるとされ、この時生じる電圧変化がEMIに繋がると考えられています。(これもどういったメカニズムでノイズ放射するかは不明です。)この電圧変化はどこの電位に対する変化なのでしょうか? 今までの記述の中なら絶対0Vのシステムグランドの電位に対するものと考えるべきでしょうか?

このようなGND絶対主義的な回路モデルを使った機器EMIの考え方に、私は違和感があります。

電磁界解析ツールで機器のフレームや基板に流れる電流を観察していくと気づくのですが、マクスウェル方程式に基づくモデルでは、GNDという概念は無いように思われます。即ちGND側の電極は単に活線となる電極の対向極でしかない、ということです。確かに、電磁界解析ツールにおけるSimモデルの境界条件として、モデル空間の周囲を0Vとすることはあっても、機器のモデルに配置する信号源の一方を接地する必要はありません。また、モデル空間の周囲を0Vにするとしても、電磁界解析する対象物のモデルに生じる電磁界に影響を与えるものではなく、またその影響が小さくなるように解析するモデルの領域の大きさを調整します。

このような電磁界解析の結果では、回路モデルで説明される前述のグランドバウンスを観測することはありません。これは信号の伝送路を構成する活線とGNDにおいて、電流が活線とGNDに対の形で流れ(但し、電流の向きが互いに逆方向)、活線とGNDそれぞれのインダクタンス成分により発生する電圧が互いにキャンセルされるためです。そのため、信号源の矩形波信号は略その電圧を維持して負荷に到達します。また、配線長にも依存しません。従って、グランドバウンスとは何か、単に回路モデルによる説明の産物なのか、少なくともEMIの原因として重要視すべきものではないでしょう。

そもそも、不要輻射は電磁波であるので、高周波ノイズの電磁場の状態によってその放射状況を考察すべきです。GND強化として、”GNDパターンを大きく・太くする”というのは高周波ノイズの電磁場の状態を変化させるための操作・調整とも考えられます。こういった考え方の詳細につきましては当社の” EMC設計 背景説明”のセミナーで説明いたします。是非とも聴講して頂きたいです。

回路図モデルによるEMIの説明にはいくつかの不都合な点があります。その最大の課題は空間を伝搬する電波についての概念がないことです。そのため、どうしても解説者にとって都合のよいイメージが入ります。コモンモードもそういった類ではないかと考えております。これについてはまた場所を改めて解説したいと思っています。

実際のEMIを考える上ではやはりマクスウェル方程式に基づくモデルの考え方の方が回路モデルによる考え方より現実に近く、EMC関係者それぞれがイメージする余地を小さくして共通の考え方を持てるのではないか、と考えています。それは即ち、EMC関係者間のミスコミュニケーションを少なくし、EMC課題の早期解決に役立つものと考えています。

この考え方は、昨今の自動車メーカーの開発プロセスとしてよく紹介されているV字設計とMBD (Model Based Development)による方法を適用したものです。製品開発において3D等の大規模な開発システム(ツール)を適用するのではなく、開発製品における開発すべき項目を、例えば構成→モジュール→デバイスのような各レベルで分解して各項目のレベルにおいて、1D-CAE(1次元的 : Computer-Aided Engineering)等を適用してモデルとして検討して、上位のモデルを実現できる下位のモデルを検討する方法であり、電子データで検証する段階をデジタル、試作による検証する段階をフィジカルと呼び、デジタルとフィジカルの結果を比較検討することにより、製品開発の高精度化・高品質化・低コスト化・スピードアップを実現するものです。 EMC設計においても、製品レベルや回路基板レベルでの3D-Simのレガシー的な適用ではなくモジュール・デバイスといったレベル、特に回路図設計段階から適用させていくべきです。Simのモデリングのためのデータインプット(Digitization)が容易で、Sim検討も関係技術者なら誰でも短時間にでき、且つ結果の共有(Digitalization)も可能で、MBDにおける上位のモデル構築にデータの紐づけとして利用することができます。例えば、回路図設計のレベルでノイズのエネルギーの低減化を検討しておけば、より上位のレベルのモデルにおいてもそのノイズのエネルギーが増大することは無いと言えます。 当社のEMC設計のアプローチは将にMBDであり、それを実現する方法としてPD、SD、WDを提案しております。上記の1D-CAEはSPICE系Simに当たります。この方法によれば、回路設計者であれば誰でもオペレーションが可能で、設計すべき事柄が明確です。また、費用的にも3Dの電磁界系Simツールに比べれば低く抑えられると共に、ライセンスの本数としても複数用意し易いです。更に、EMI低減効果は確実に出ます。(その状況は電磁界Sim等で確認することが可能)

この考え方は、昨今の自動車メーカーの開発プロセスとしてよく紹介されているV字設計とMBD (Model Based Development)による方法を適用したものです。製品開発において3D等の大規模な開発システム(ツール)を適用するのではなく、開発製品における開発すべき項目を、例えば構成→モジュール→デバイスのような各レベルで分解して各項目のレベルにおいて、1D-CAE(1次元的 : Computer-Aided Engineering)等を適用してモデルとして検討して、上位のモデルを実現できる下位のモデルを検討する方法であり、電子データで検証する段階をデジタル、試作による検証する段階をフィジカルと呼び、デジタルとフィジカルの結果を比較検討することにより、製品開発の高精度化・高品質化・低コスト化・スピードアップを実現するものです。 EMC設計においても、製品レベルや回路基板レベルでの3D-Simのレガシー的な適用ではなくモジュール・デバイスといったレベル、特に回路図設計段階から適用させていくべきです。Simのモデリングのためのデータインプット(Digitization)が容易で、Sim検討も関係技術者なら誰でも短時間にでき、且つ結果の共有(Digitalization)も可能で、MBDにおける上位のモデル構築にデータの紐づけとして利用することができます。例えば、回路図設計のレベルでノイズのエネルギーの低減化を検討しておけば、より上位のレベルのモデルにおいてもそのノイズのエネルギーが増大することは無いと言えます。 当社のEMC設計のアプローチは将にMBDであり、それを実現する方法としてPD、SD、WDを提案しております。上記の1D-CAEはSPICE系Simに当たります。この方法によれば、回路設計者であれば誰でもオペレーションが可能で、設計すべき事柄が明確です。また、費用的にも3Dの電磁界系Simツールに比べれば低く抑えられると共に、ライセンスの本数としても複数用意し易いです。更に、EMI低減効果は確実に出ます。(その状況は電磁界Sim等で確認することが可能)