冬場の静電気は誰もが経験するいやな現象でしょう。特にお風呂に入る前の脱衣時に衣類と衣類のこすれで聞こえる”パチパチ”という音(暗いと光も見えます)や、脱いだ衣類がヒトの皮膚に”ゾアー”とした感じを与えるのも嫌な感じです。

”冬は乾燥するから”との思いから”静電気発生”⇐”乾燥(低湿度)が原因”と考える方も多いでしょう。確かに湿度、即ち大気中の水蒸気量が静電気の発生に影響します。

ではどう影響するでしょうか?

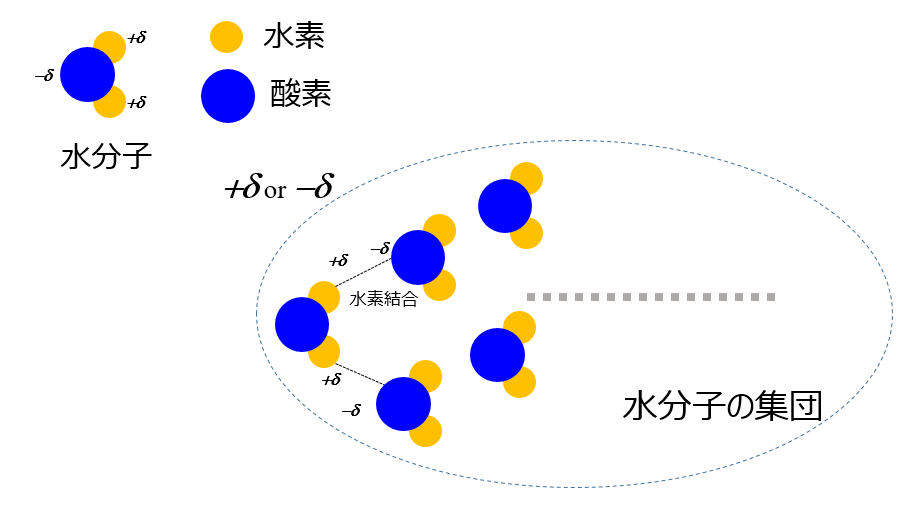

水蒸気である水分子は水素原子と酸素原子により構成され、水分子全体としては電気的に中性ですが、図に示すように電気的な偏りを持っており極性分子となります。この水分子は大気中に十分にランダムに存在するのではなく、水分子同士の極性(水素結合の引力)によってある程度集団的に存在し、その集団は全体として正、又は負の極性をもちます。

それに対し大気中にある物体はその表面に電位を持つので、その電位に反応して水分子の集団が物体の表面に近づき、物体の表面の電位を下げる作用を示します。これは静電気メーターで物体の表面電位を測定する際、測定する物体の表面に息を吹きかけて測定を行うと測定値が0V側に近づくことで確認できます。

よって、湿度が高い時は上記の作用によりあらゆる物体の表面電位は0V側に変化するので、物体間における各表面の電位の差(電位勾配)も小さくなるので、静電気(火花放電)は発生しにくくなります。逆に、乾燥する(湿度が低い)と、水分子の量が減るので物体の表面電位を下げる作用が小さくなり、物体間の電位勾配が小さくなりづらく、火花放電は発生し易くなります。

それ故、”冬場→乾燥→静電気”は自然の静電気(ESD)発生の正しい関連性です。

しかしその一方で、前述したように水分子は極性分子なので電位勾配を生じさせている物体の表面付近に存在する場合、その物体表面に向かって加速し衝突(スパッタ)します。このスパッタが生じると特に物体が導体である場合は物体内部の電子が大気に飛び出し、物体表面付近にある気体分子をイオン化させ、プラズマを生じ、これが火花放電になります。

ESD試験であるIEC61000-4-2の気中放電試験ではESDガンと被試験機器の間の火花放電は湿度が高い時程発生し易くなり、被試験機器の不具合を発生させます。この現象については多くのEMC関係の方々が経験しているでしょう。これは、IEC61000-4-2の試験が自然の静電気ではなく、ESDガンの電源よりESDガンのガン先(放電チップ)と被試験機器の筐体(GND)に回路形態で安定的に電力(電圧・電流)を供給しているためで、放電チップと被試験機器のGNDの電位勾配は周囲の湿度に関係なく安定的に印加され、それにより水分子は放電チップ或いは被試験機器のGNDに向かって加速・衝突を起こし、火花放電を発生させます。そのため、水分子の数が増せば(湿度が高ければ)火花放電を発生させ易くなります。

私見ですが、IEC61000-4-2の気中放電の試験は試験条件として湿度の範囲は30~60%とされているので、できるだけ30%側ですべきだと考えています。その根拠としては、

①試験条件を満たして試験を行っていること、

②気中放電の試験は機器の実際の使用状態で生じるESDとはかなり異なっていること、

③試験ではESDガンの設定電圧を高め(1.2~1.5倍)にして試験を行っていること、

などからです。

機器の気中放電試験の未検討は許されませんが、ESDガンによる気中放電は被試験機器にとっては厳しい試験であり、機器へのダメージが大きく、試験により破損に至る場合もあります。ESD課題の対策作業の際、過多なESDガンパルスの印加により被試験機器の破損に気づかず対策作業が泥沼化するケースもあります。

是非ESDの試験、特に気中放電の試験は湿度にも注意を払って行ってください。

関連ページ・・・こちらもご覧ください。

27. ESD試験時の2次放電発生の予見をsimで確認・・・これが不具合原因!

”ESD及び静電気による機器・装置の不具合解析に当社のESD2”

ESDスキャナで観測。でもやっぱり対策はいつものGND強化?

”4. ESD及び静電気による機器・装置の不具合解析に当社のESD2”

“ESD試験(IEC61000-4-2)対策に関する技術資料”